这次设计一个DDS信号发生器。该设计的特点有:

- 双通道的DA输出,可以调节频率、相位、和波形(正弦波、方波、三角波)。

- 拥有相位重置的功能,能够同时重置两个输出波形的相位。

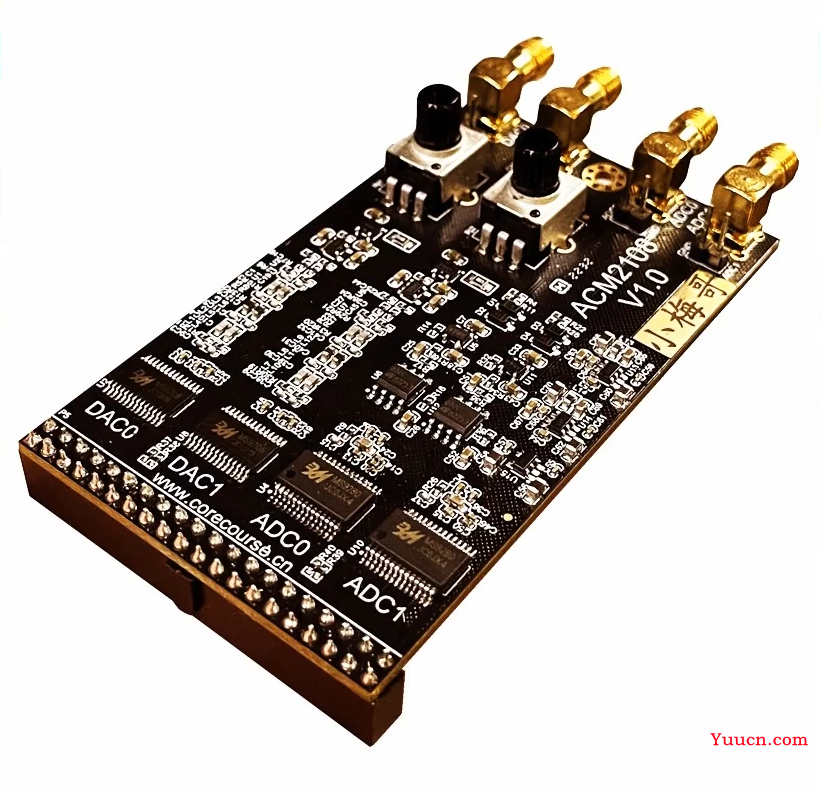

本次采用的是小梅哥的ACM2108模块。该模块有两个通道的ADC和两个通道的DAC。

本次设计的前置是DDS基本模块,具体可点击链接查看。DDS基本模块在加入了装有正弦波数据的ROM的基础上,再添加三角波和方波的数据的ROM,从而能够切换输出的波形。

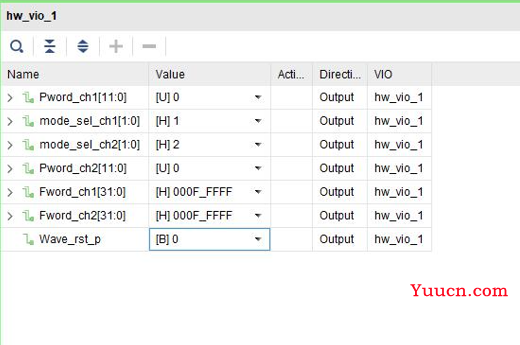

通过调用VIO这个IP核,设置输出信号的频率、相位和波形。

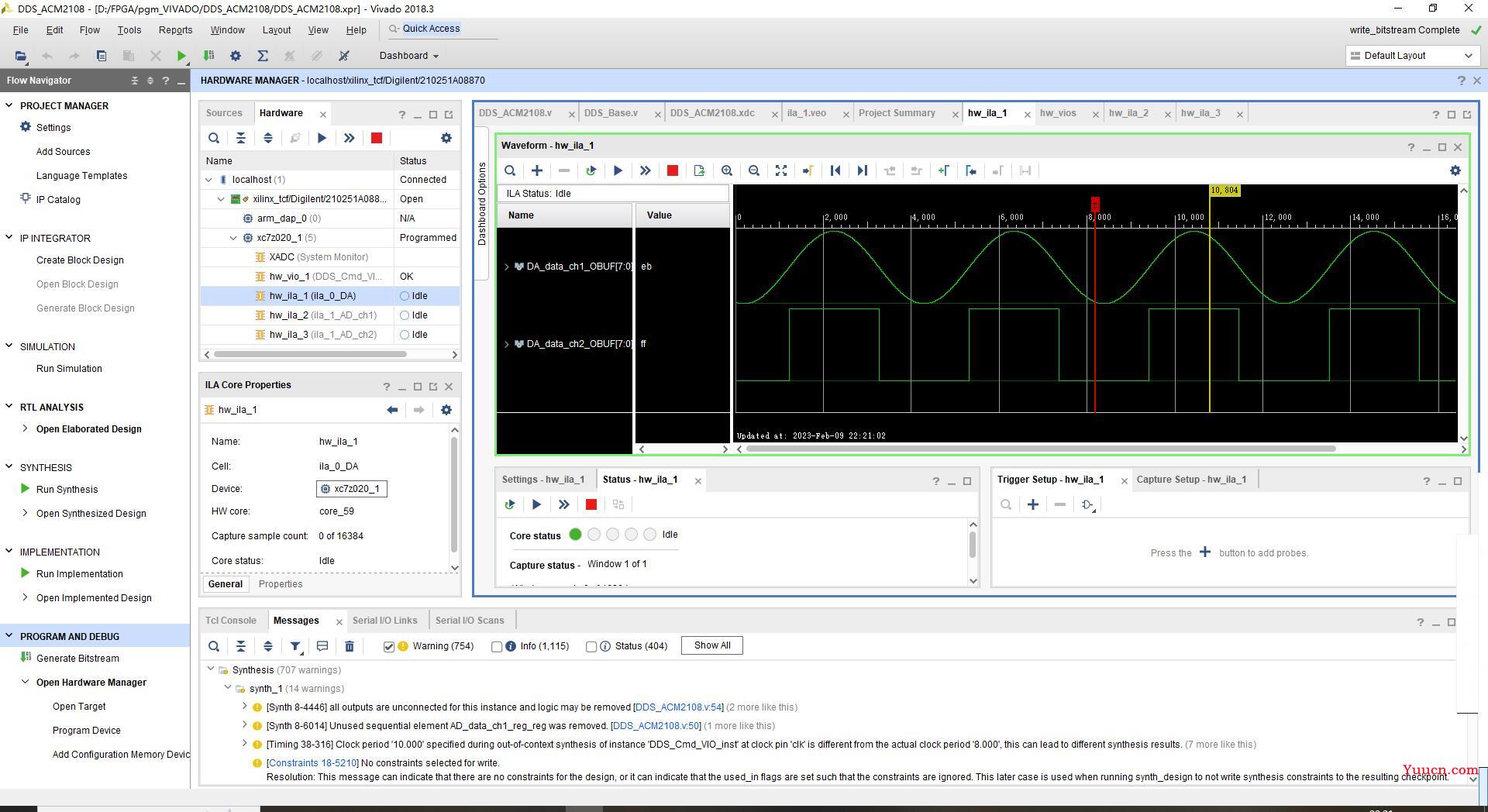

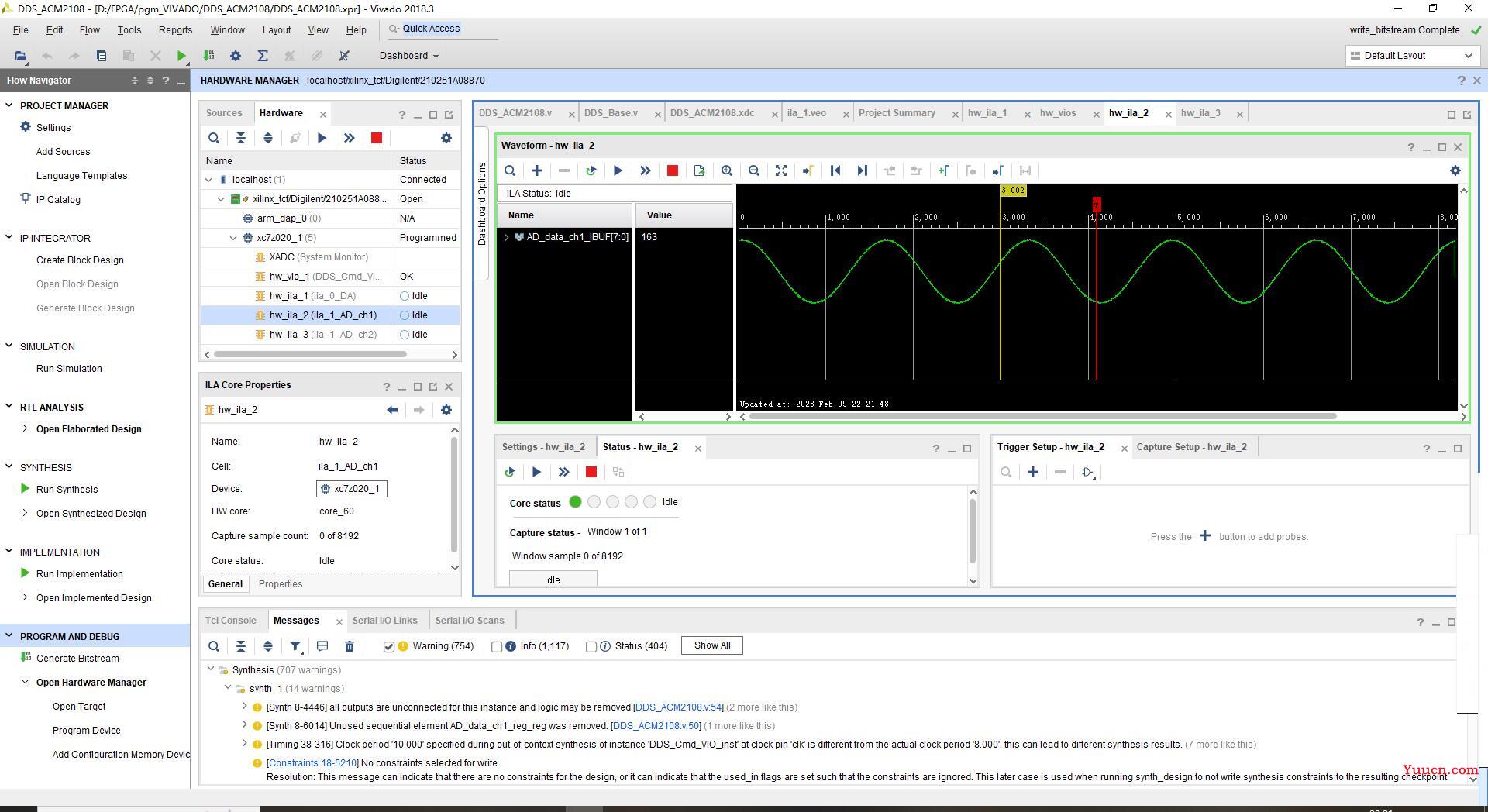

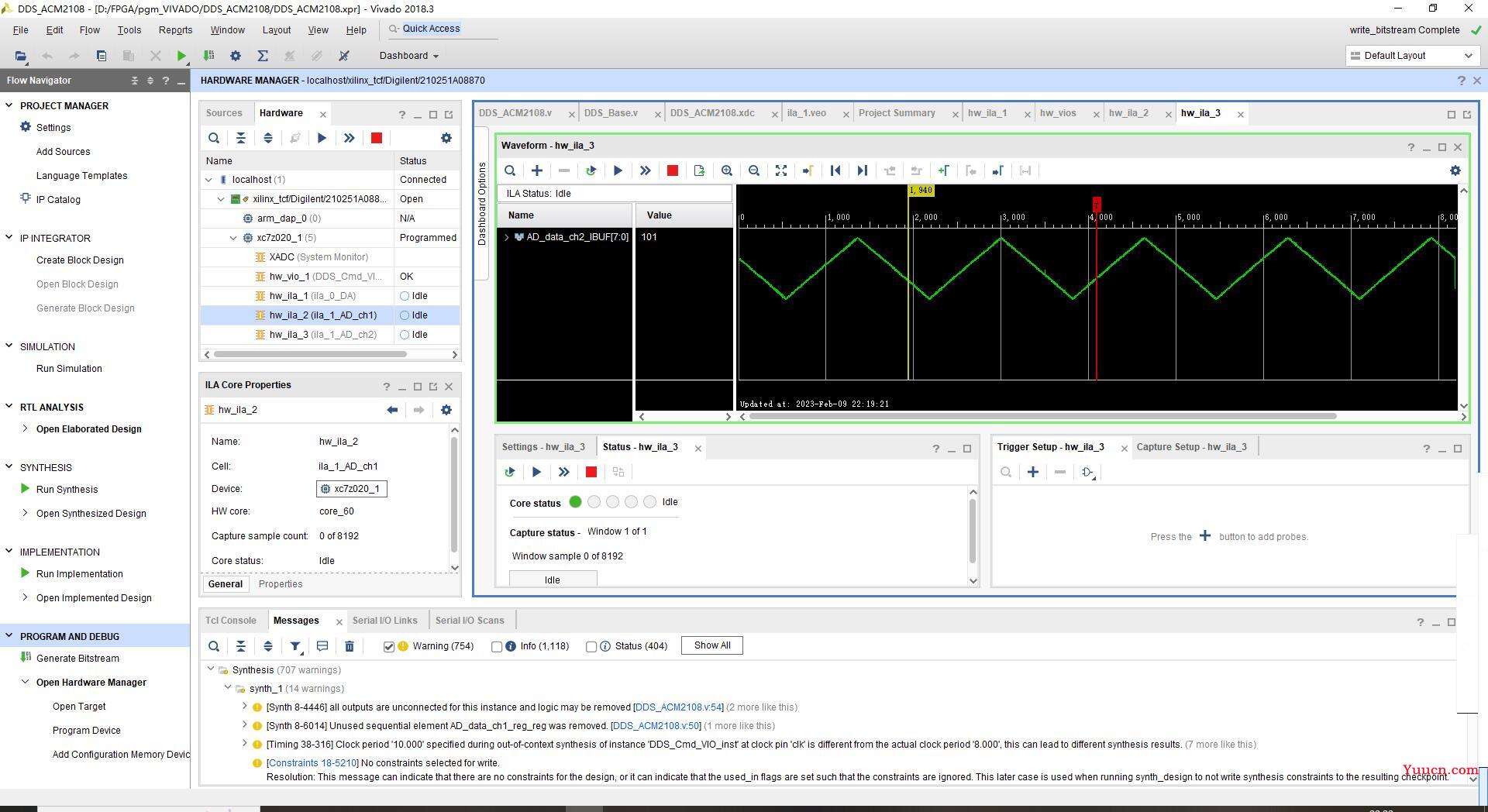

然后通过LIA这个IP核,去观察数据波形。

一、模块代码

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: GDUT

// Engineer: Lclone

//

// Create Date: 2023/02/02 22:34:21

// Design Name: DDS_ACM2108

// Module Name: DDS_ACM2108

// Project Name: DDS_ACM2108

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module DDS_ACM2108(

input Clk,

input Rst_n,

output DA_Clk_ch1,

output [7:0] DA_data_ch1,

output DA_Clk_ch2,

output [7:0] DA_data_ch2,

output AD_Clk_ch1,

input [7:0] AD_data_ch1,

output AD_Clk_ch2,

input [7:0] AD_data_ch2

);

wire Clk_125M;

wire [31:0] Fword_ch1;

wire [11:0] Pword_ch1;

wire [ 1:0] mode_sel_ch1;

wire [31:0] Fword_ch2;

wire [11:0] Pword_ch2;

wire [ 1:0] mode_sel_ch2;

reg [7:0] AD_data_ch1_reg;

reg [7:0] AD_data_ch2_reg;

wire Wave_rst_p;

always@(posedge Clk)begin

AD_data_ch1_reg <= AD_data_ch1;

AD_data_ch2_reg <= AD_data_ch2;

end

ila_0 ila_0_DA (

.clk(Clk_125M), // input wire clk

.probe0(DA_data_ch1), // input wire [7:0] probe0

.probe1(DA_data_ch2) // input wire [7:0] probe1

);

ila_1 ila_1_AD_ch1 (

.clk(Clk), // input wire clk

.probe0(AD_data_ch1) // input wire [7:0] probe0

);

ila_1 ila_1_AD_ch2 (

.clk(Clk), // input wire clk

.probe0(AD_data_ch2) // input wire [7:0] probe0

);

clk_wiz_0 clk_wiz_0_inst (

// Clock out ports

.clk_out1(Clk_125M), // output clk_out1

// Clock in ports

.clk_in1(Clk)); // input clk_in1

DDS_Cmd_VIO DDS_Cmd_VIO_inst (

.clk(Clk_125M), // input wire clk

.probe_out0(Fword_ch1), // output wire [31 : 0] probe_out0

.probe_out1(Pword_ch1), // output wire [11 : 0] probe_out1

.probe_out2(mode_sel_ch1), // output wire [1 : 0] probe_out2

.probe_out3(Fword_ch2), // output wire [31 : 0] probe_out3

.probe_out4(Pword_ch2), // output wire [11 : 0] probe_out4

.probe_out5(mode_sel_ch2), // output wire [1 : 0] probe_out5

.probe_out6(Wave_rst_p) // output wire [1 : 0] probe_out5

);

DDS_Base DDS_Base_ch1(

.Clk (Clk_125M),

.Rst_n (Rst_n & ~Wave_rst_p),

.Fword (Fword_ch1),

.Pword (Pword_ch1),

.mode_sel (mode_sel_ch1),

.DA_Clk (DA_Clk_ch1),

.Signal_data (DA_data_ch1)

);

DDS_Base DDS_Base_ch2(

.Clk (Clk_125M),

.Rst_n (Rst_n & ~Wave_rst_p),

.Fword (Fword_ch2),

.Pword (Pword_ch2),

.mode_sel (mode_sel_ch2),

.DA_Clk (DA_Clk_ch2),

.Signal_data (DA_data_ch2)

);

assign AD_Clk_ch1 = Clk;

assign AD_Clk_ch2 = Clk;

endmodule

二、上板结果

我将ACM2108的ad接口与da接口进行连接,然后通过ila观察AD和DA的波形来观察设计是否成功。

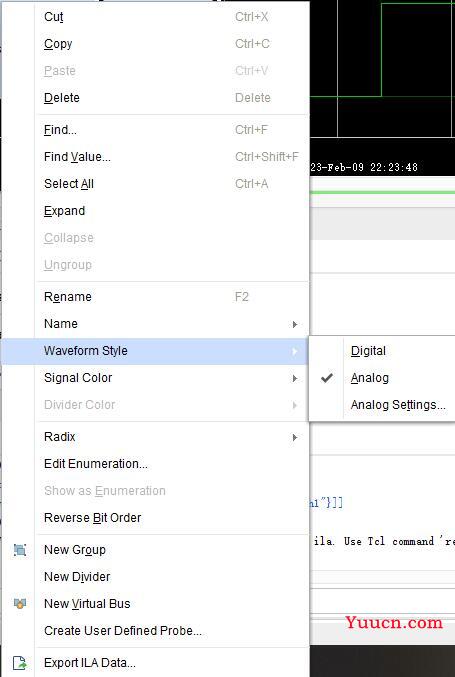

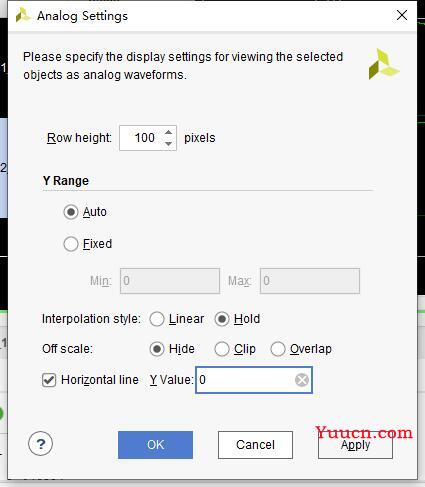

在观察方波信号的时候,vivado可能会帮我们的波形做处理,导致我们观察的方波变成三角波,这里我们在Analog Settings里将Interpolation style改为Hold即可设置为正常显示的波形。

以下是上板后的结果:

程序上板后,可以输出频率和相位可调的正弦波、方波、三角波。